- SYNCHRONOUS SEQUENTIAL SYSTEMS

- MEALY AND MOORE MACHINES

- TIME BEHAVIOR

- STATE MINIMIZATION

1

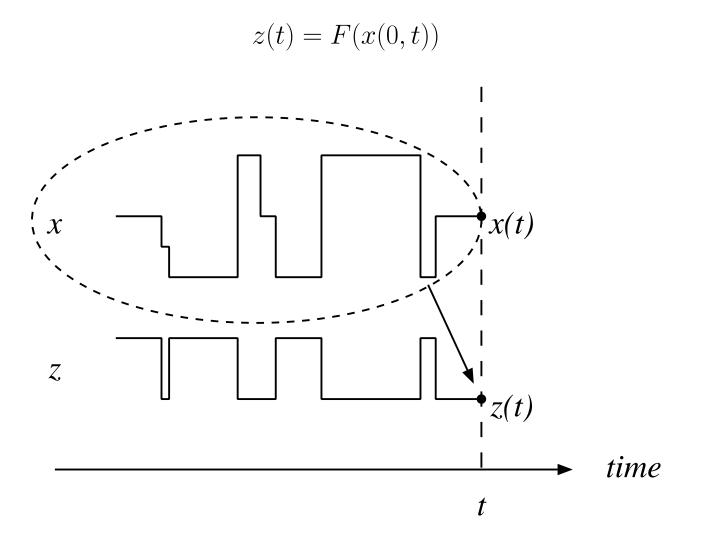

Figure 7.1: INPUT AND OUTPUT TIME FUNCTIONS.

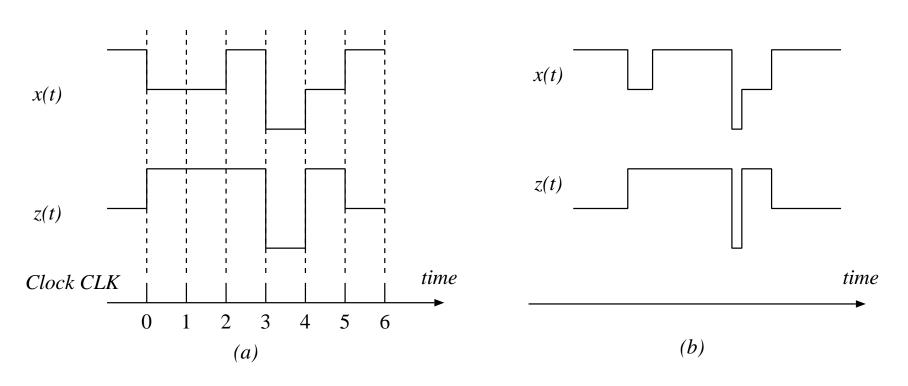

Figure 7.2: a) SYNCHRONOUS BEHAVIOR. b) ASYNCHRONOUS BEHAVIOR.

- CLOCK

- I/O SEQUENCE  $x(t_1, t_2)$

$$x(2,5) = aabc$$

$z(2,5) = 1021$

| Х | 1638753 |

|---|---------|

| у | 3652425 |

| Ζ | 5291178 |

• LEAST-SIGNIFICANT DIGIT FIRST (at t=0)

| t                        | 0 | 1 | 2 | 3 | 4 | 5 | 6 |

|--------------------------|---|---|---|---|---|---|---|

| x(t)                     | 3 | 5 | 7 | 8 | 3 | 6 | 1 |

| $\frac{t}{x(t)}$<br>y(t) |   |   |   |   |   |   |   |

| z(t)                     | 8 | 7 | 1 | 1 | 9 | 2 | 5 |

#### STATE DESCRIPTION

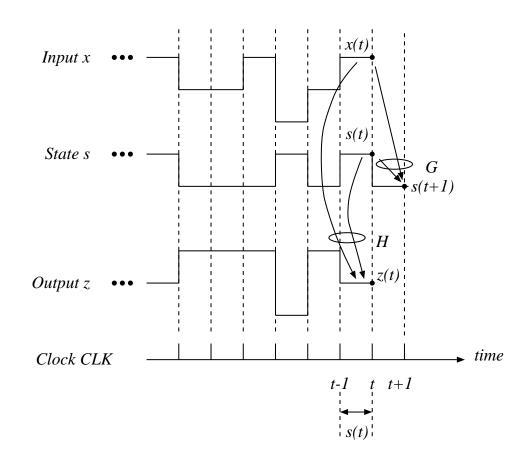

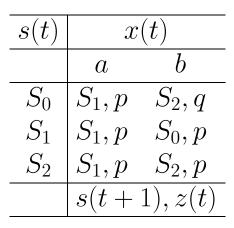

Figure 7.3: OUTPUT AND STATE TRANSITION FUNCTIONS

$\begin{array}{lll} \mbox{Input:} & x(t), y(t) \in \{0, 1, ..., 9\} \\ \mbox{Output:} & z(t) \in \{0, 1, ..., 9\} \\ \mbox{State:} & s(t) \in \{0, 1\} \mbox{ (the carry)} \\ \mbox{Initial state:} & s(0) = 0 \\ \end{array}$

Functions: The transition and output functions are

$$s(t+1) = \begin{cases} 1 & \text{if } x(t) + y(t) + s(t) \ge 10 \\ 0 & \text{otherwise} \end{cases}$$

$$z(t) = (x(t) + y(t) + s(t)) \mod 10$$

EXAMPLE:

| t                                                                        | 0 | 1 | 2 | 3 | 4 | 5 | 6 |

|--------------------------------------------------------------------------|---|---|---|---|---|---|---|

| x(t)                                                                     | 3 | 5 | 7 | 8 | 3 | 6 | 1 |

| y(t)                                                                     | 5 | 2 | 4 | 2 | 5 | 6 | 3 |

| s(t)                                                                     | 0 | 0 | 0 | 1 | 1 | 0 | 1 |

| $     \begin{array}{r} x(t) \\ y(t) \\ \hline s(t) \\ z(t) \end{array} $ | 8 | 7 | 1 | 1 | 9 | 2 | 5 |

TIME-BEHAVIOR SPECIFICATION:

$\begin{array}{lll} \mbox{Input:} & x(t) \in \{a,b\} \\ \mbox{Output:} & z(t) \in \{0,1\} \end{array}$

Function:  $z(t) = \begin{cases} 1 & \text{if } x(0,t) \text{ contains an even number of } b's \\ 0 & \text{otherwise} \end{cases}$

I/O SEQUENCE:

| Input:         | $x(t) \in \{a, b\}$             |

|----------------|---------------------------------|

| Output:        | $z(t) \in \{0, 1\}$             |

| State:         | $s(t) \in \{\text{EVEN, ODD}\}$ |

| Initial state: | s(0) = EVEN                     |

#### Functions: Transition and output functions

| PS   | x(t) = a | x(t) = b  |

|------|----------|-----------|

| EVEN | EVEN, 1  | ODD, 0    |

| ODD  | odd, 0   | EVEN, $1$ |

|      | NS,      | z(t)      |

Mealy machine

$$z(t) = H(s(t), x(t))$$

$$s(t+1) = G(s(t), x(t))$$

Moore machine

$$z(t) = H(s(t))$$

$$s(t+1) = G(s(t), x(t))$$

### • EQUIVALENT IN CAPABILITIES

Introduction to Digital Systems

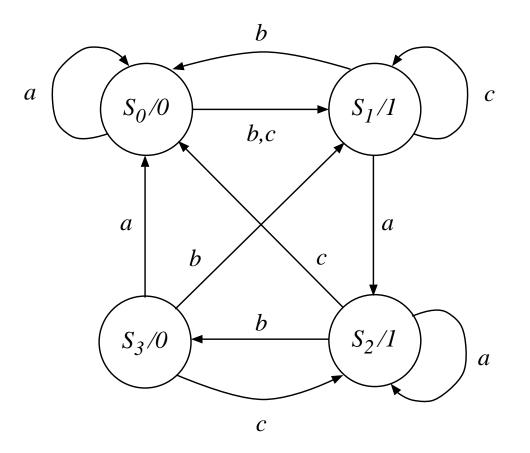

| Input:         | $x(t) \in \{a, b, c\}$            |

|----------------|-----------------------------------|

| Output:        | $z(t) \in \{0,1\}$                |

| State:         | $s(t) \in \{S_0, S_1, S_2, S_3\}$ |

| Initial state: | $s(0) = S_0$                      |

Functions: Transition and output functions:

| PS    | Input |       |       |        |

|-------|-------|-------|-------|--------|

|       | a     | b     | С     |        |

| $S_0$ | $S_0$ | $S_1$ | $S_1$ | 0      |

| $S_1$ | $S_2$ | $S_0$ | $S_1$ | 1      |

| $S_2$ | $S_2$ | $S_3$ | $S_0$ | 1      |

| $S_3$ | $S_0$ | $S_1$ | $S_2$ | 0      |

|       | NS    |       |       | Output |

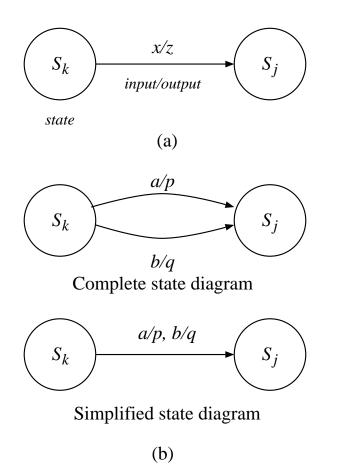

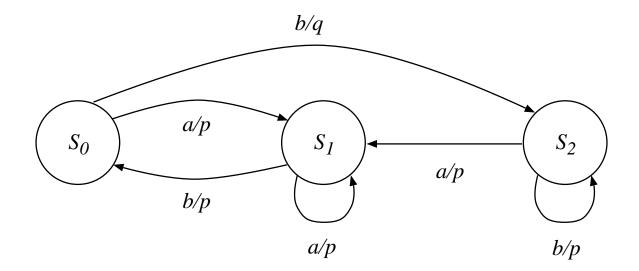

• STATE DIAGRAM

Figure 7.4: (a) STATE DIAGRAM REPRESENTATION. (b) SIMPLIFIED STATE DIAGRAM NOTATION.

Functions: The transition and output functions are

Figure 7.5: STATE DIAGRAM FOR EXAMPLE 7.6.

Figure 7.6: STATE DIAGRAM FOR EXAMPLE 7.5

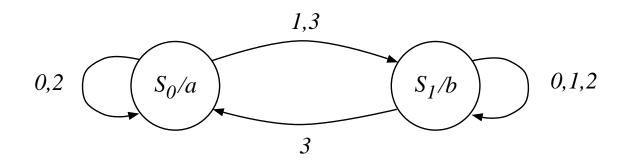

Input:

$$x(t) \in \{0, 1, 2, 3\}$$

Output:

$z(t) \in \{a, b\}$

State:

$s(t) \in \{S_0, S_1\}$

Initial state:

$s(0) = S_0$

Functions: The transition and output functions are

$$s(t+1) = \begin{cases} S_0 \text{ if } (s(t) = S_0 \\ \text{ and } [x(t) = 0 \text{ or } x(t) = 2]) \\ \text{ or } (s(t) = S_1 \text{ and } x(t) = 3) \\ S_1 \text{ otherwise} \end{cases}$$

$$z(t) = \begin{cases} a \text{ if } s(t) = S_0 \\ b \text{ if } s(t) = S_1 \end{cases}$$

### STATE NAMES

#### Example 7.8: INTEGERS AS STATE NAMES

#### A MODULO-64 COUNTER

Functions: The transition and output functions are

$$s(t+1) = [s(t) + x(t)] \mod 64$$

$$z(t) = s(t)$$

Input:

$$e(t) \in \{1, 2, ..., 55\}$$

Output: $z(t) \in \{0, 1, 2, ..., 55\}$ State: $\underline{s}(t) = (s_{55}, ..., s_1), s_i \in \{0, 1, 2, ..., 99\}$ Initial state: $\underline{s}(0) = (0, 0, ..., 0)$

Functions: The transition and output functions are

$$s_i(t+1) = \begin{cases} [s_i(t)+1] \mod 100 & \text{if} \quad e(t) = i \\ i = 1, 2, \dots, 55 \\ s_i(t) & \text{otherwise} \end{cases}$$

$$z(t) = \begin{cases} i & \text{if} \quad e(t) = i \text{ and } s_i(t) = 99 \\ 0 & \text{otherwise} \end{cases}$$

• STATE DESCRIPTION  $\Rightarrow$  I/O SEQUENCE (Example 7.10)

Initial state:  $s(0) = S_2$ Functions: Transition and output functions are

| $\overline{P}$ | S            | x(t)   |       |           |          |

|----------------|--------------|--------|-------|-----------|----------|

|                |              | a      | b     | С         |          |

| S              | 0            | $S_0$  | $S_1$ | $S_1$     | p        |

| S              | 1            | $S_2$  | $S_0$ | $S_1$     | q        |

| S              | $2^{2}$      | $S_2$  | $S_3$ | $S_0$     | q        |

| S              | $3^{\prime}$ | $S_0$  | $S_1$ | $S_2$     | p        |

|                |              |        | NS    | 1         | z(t)     |

| t              | 0            | 1      | . 2   | 2 3       | 4        |

| x              | a            | b b    | ) (   | e a       | ,        |

| S              | $S_{2}$      | $_2 S$ | $S_2$ | $S_3 S_2$ | $_2 S_2$ |

| $\mathcal{Z}$  | q            | q      | r p   | p q       |          |

• NOT ALL TIME-BEHAVIORS ARE REALIZABLE:

$z(t) = \begin{cases} 1 & \text{if } x(0,t) \text{ has same number of } 0'\text{s and } 1'\text{s} \\ 0 & \text{otherwise} \end{cases}$

s(t) = DIFFERENCE BETWEEN NUMBER OF 1'S AND 0'S

$$s(t+1) = \begin{cases} s(t) + 1 & \text{if} \quad x(t) = 1\\ s(t) - 1 & \text{otherwise} \end{cases}$$

$$z(t) = \begin{cases} 1 & \text{if} \quad s(t) = 0 \\ 0 & \text{otherwise} \end{cases}$$

$\Rightarrow$  DIFFERENCE UNBOUNDED: NOT A FINITE-STATE SYSTEM

## 1. DETERMINE A SET OF STATES REPRESENTING REQUIRED EVENTS

### 2. DETERMINE THE TRANSITION FUNCTION

# 3. DETERMINE THE OUTPUT FUNCTION

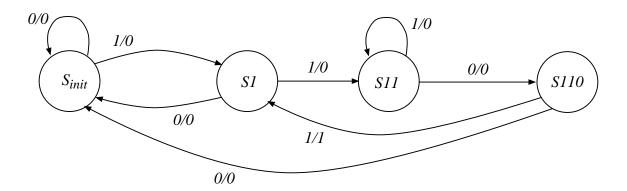

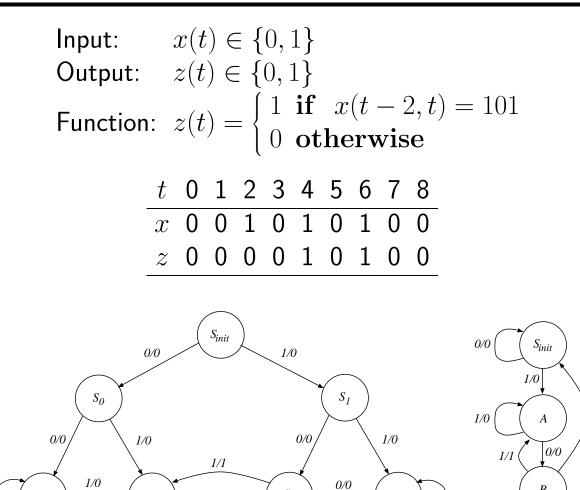

• Example 7.11

$$\begin{array}{ll} \mathsf{Input:} & x(t) \in \{0,1\} \\ \mathsf{Output:} & z(t) \in \{0,1\} \\ \mathsf{Function:} & z(t) = \left\{ \begin{array}{ll} 1 & \mathbf{if} & x(t-3,t) = 1101 \\ 0 & \mathbf{otherwise} \end{array} \right. \end{array}$$

• PATTERN DETECTOR  $\Rightarrow$  DETECT SUBPATTERNS

State indicates that

- $S_{init}$  | Initial state; also no subpattern

- $S_1$  | First symbol (1) of pattern has been detected

- $S_{11}$  | Subpattern 11 has been detected

- $S_{110}$  | Subpattern 110 has been detected

Figure 7.8: STATE DIAGRAM FOR Example 7.11

$$z(t) = F(x(t - m + 1, t))$$

Example 7.12:

$$z(t) = \begin{cases} p & \text{if } x(t-3,t) = aaba \\ q & \text{otherwise} \end{cases}$$

## $\Rightarrow$ FINITE MEMORY OF LENGTH FOUR

- ALL FINITE-MEMORY MACHINES ARE FS SYSTEMS

- NOT ALL FS SYSTEMS ARE FINITE MEMORY

$$z(t) = \begin{cases} 1 & \text{if number of } 1'\text{s in } x(0,t) \text{ is even} \\ 0 & \text{otherwise} \end{cases}$$

- THE STATE DESCRIPTION IS PRIMARY

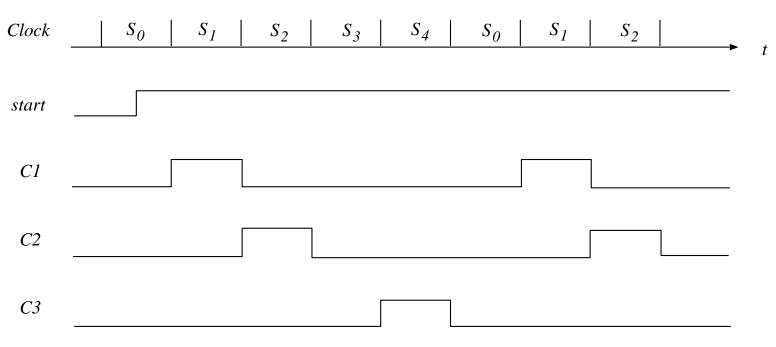

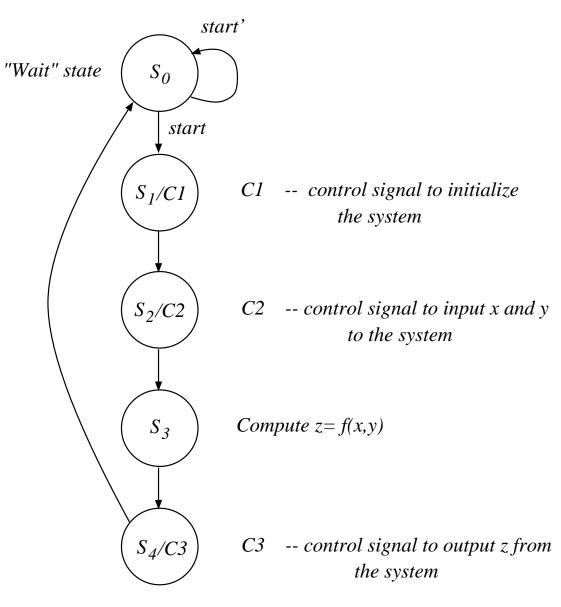

- FSM PRODUCING CONTROL SIGNALS

- CONTROL SIGNALS DETERMINE ACTIONS PERFORMED IN OTHER PARTS OF SYSTEM

- *AUTONOMOUS*: FIXED SEQUENCE OF STATES, INDEPENDENT OF INPUTS

Figure 7.9: AUTONOMOUS CONTROLLER: TIMING DIAGRAM.

Figure 7.10: AUTONOMOUS CONTROLLER: STATE DIAGRAM.

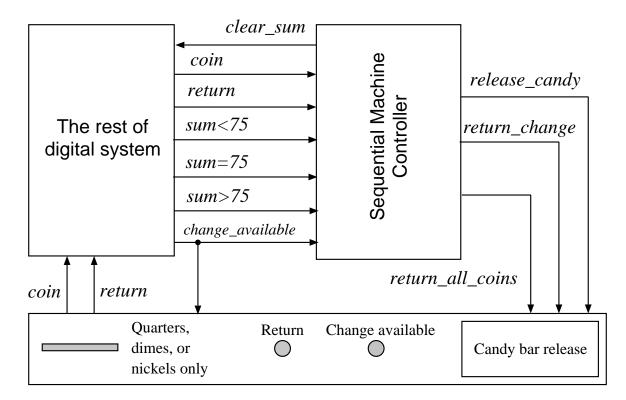

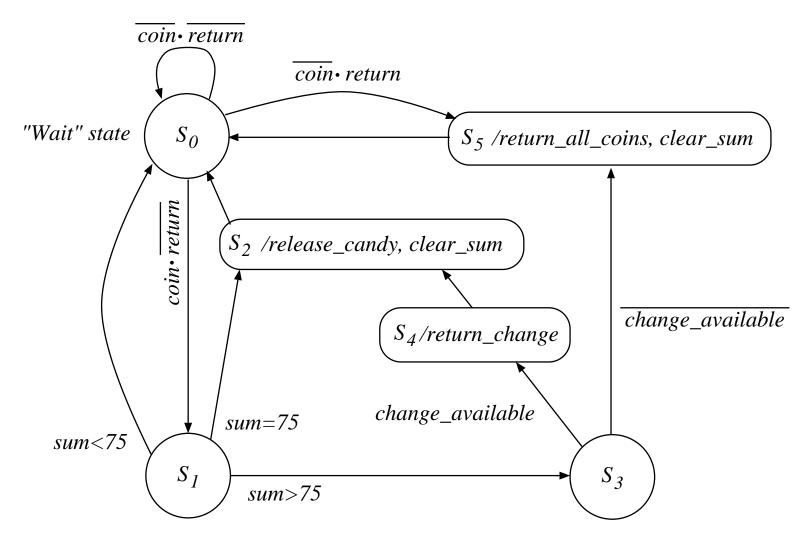

Note:  $coin \cdot return = 0$

Figure 7.11: CONTROLLER FOR SIMPLE VENDING MACHINE: BLOCK DIAGRAM.

Figure 7.12: CONTROLLER FOR SIMPLE VENDING MACHINE: STATE DIAGRAM.

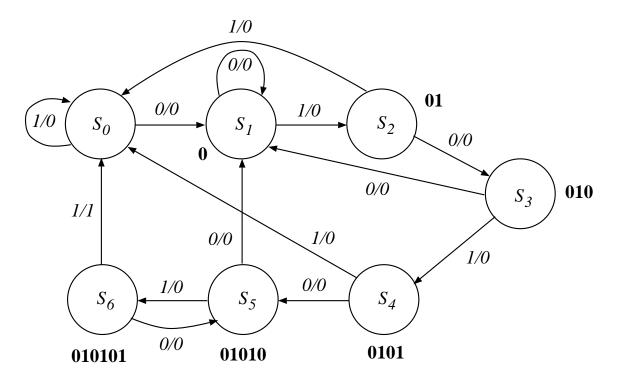

Figure 7.13: a) STATE DIAGRAM WITH REDUNDANT STATES; b) REDUCED STATE DIAGRAM

$S_{10}$

1/0

$S_{11}$

1/0

Introduction to Digital Systems

0/0

$S_{00}$

*S*<sub>01</sub>

0/0

0/0

(a)

7 – Specification of Sequential Systems

0/0

В

(b)

28

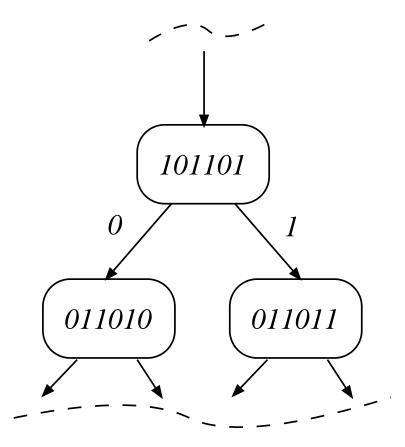

### • k-DISTINGUISHABLE STATES: DIFF. OUTPUT SEQUENCES

$z(x(t, t + k - 1), S_v) \neq z(x(t, t + k - 1), S_w)$

EXAMPLE:

$\begin{array}{cccc} {\sf State} & x(3,7) & z(3,7) \\ S_1 & 0210 & 0011 \\ S_3 & 0210 & 0001 \end{array}$

- k-EQUIVALENT STATES: NOT DISTINGUISHABLE FOR SEQUENCES OF LENGTH k

- $P_k$ : PARTITION OF STATES INTO k-EQUIVALENT CLASSES

- $\bullet$  EQUIVALENT STATES NOT DISTINGUISHABLE FOR ANY k

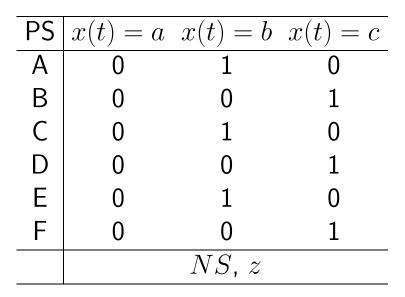

| Input:         | $x(t) \in \{a, b, c\}$          |

|----------------|---------------------------------|

| Output:        | $z(t) \in \{0, 1\}$             |

| State:         | $s(t) \in \{A, B, C, D, E, F\}$ |

| Initial state: | s(0) = A                        |

### Functions: TRANSITION AND OUTPUT

• A and B ARE 1-DISTINGUISHABLE BECAUSE

$z(b,A) \neq z(b,B)$

•  $A \text{ and } C \text{ ARE } 1\text{-} EQUIVALENT BECAUSE}$

$z(x(t), A) = z(x(t), C), \quad for \ all \ x(t) \in I$

• A and C ARE ALSO 2-EQUIVALENT BECAUSE

$$\begin{array}{rcl} z(aa,A) &=& z(aa,C) &=& 00 \\ z(ab,A) &=& z(ab,C) &=& 01 \\ z(ac,A) &=& z(ac,C) &=& 00 \\ z(ba,A) &=& z(ba,C) &=& 10 \\ z(bb,A) &=& z(bb,c) &=& 10 \\ z(bc,A) &=& z(bc,C) &=& 11 \\ z(ca,A) &=& z(ca,C) &=& 00 \\ z(cb,A) &=& z(cc,C) &=& 01 \end{array}$$

```

Obtaining P_1: DIRECTLY FROM OUTPUT FUNCTION

From P_i to P_{i+1} ...

```

1.  $P_{i+1}$  IS A REFINEMENT OF  $P_i$ (states (i+1)-equiv. must also be i-equiv.)

$\begin{array}{ccc} P_i & (A,B,C)(D) \\ & \text{possible} & \text{not possible} \\ P_{i+1} & (A,C)(B)(D) & (A,D)(B)(C) \end{array}$

FOR (i+1)-EQUIVALENT STATES  $S_v$  and  $S_w$

$$z(x(t,t+i),S_v) = z(x(t,t+i),S_w)$$

FOR ARBITRARY x(t, t + i)THEN  $z(x(t, t + i - 1), S_v) = z(x(t, t + i - 1), S_w)$ EXAMPLE:  $z(abcd, S_v) = z(abcd, S_w) = 1234$ THEN  $z(abc, S_v) = z(abc, S_w) = 123$

Introduction to Digital Systems

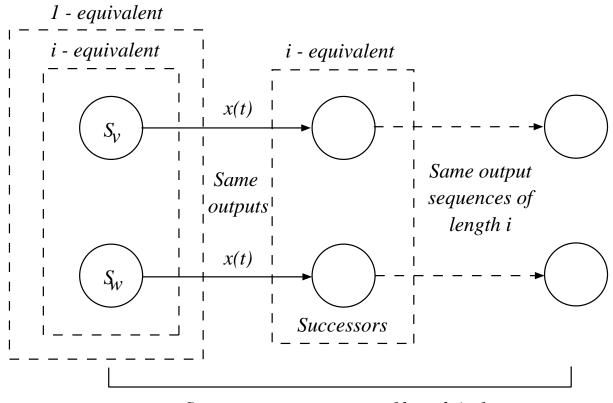

- 2. TWO STATES ARE (i+1)-EQUIVALENT IF AND ONLY IF

- a) THEY ARE i-EQUIVALENT, and

```

b) FOR ALL x \in \mathit{I} , the corresponding next states are i-equivalent

```

PROOF:

IF PART:

- SINCE THE STATES ARE i-EQUIVALENT, THEY ARE ALSO 1-EQUIVALENT

- THEREFORE, IF THE NEXT STATES ARE i-EQUIVALENT, THE STATES ARE (i+1)-EQUIVALENT

Same output sequences of length i+1

Figure 7.14: ILLUSTRATION OF (i + 1)-EQUIVALENCE RELATION.

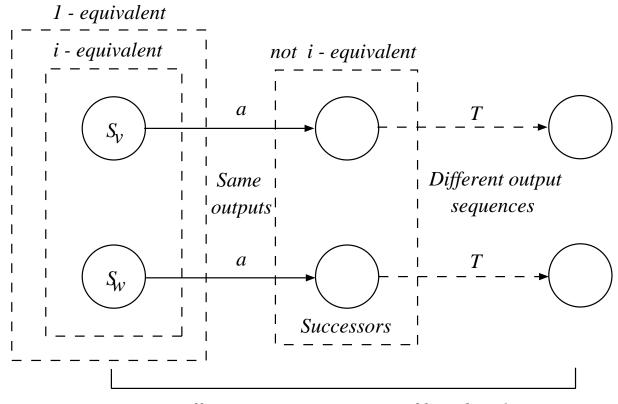

ONLY IF PART: BY CONTRADICTION

• IF FOR SOME INPUT a THE NEXT STATES ARE NOT i-EQUIVALENT THEN THERE EXISTS A SEQUENCE T OF LENGTH i SUCH THAT THESE NEXT STATES ARE DISTINGUISHABLE.

THEREFORE,

$z(aT, S_v) \neq z(aT, S_w)$

$\rightarrow S_v$  AND  $S_w$  NOT (i+1)-EQUIVALENT

Different output sequences of length i+1

Figure 7.15: ILLUSTRATION OF (i + 1)-EQUIVALENCE RELATION.

- STOP WHEN  $P_{i+1}$  IS THE SAME AS  $P_i$

- THIS IS THE EQUIVALENCE PARTITION

- THE PROCESS ALWAYS TERMINATES

1. OBTAIN  $P_1$  (look at the outputs)

## 2. OBTAIN $P_{i+1}$ FROM $P_i$ BY GROUPING STATES THAT ARE *i*-EQUIVALENT AND WHOSE CORRESPONDING SUCCESSORS ARE *i*-EQUIVALENT

- 3. TERMINATE WHEN  $P_{i+1} = P_i$

- 4. WRITE THE REDUCED TABLE

• 1-EQUIVALENT IF SAME "row pattern"

$P_1 = (A, C, E) \quad (B, D, F)$

- NUMBER THE CLASSES IN  $P_1$

- TWO STATES ARE IN THE SAME CLASS OF  $P_2$ IF THEIR SUCCESSOR COLUMNS HAVE THE SAME NUMBERS

|               | 1   |        |    | 2            |            |    |

|---------------|-----|--------|----|--------------|------------|----|

| $P_1$         | (А, | C,     | E) | ( <i>B</i> , | <i>D</i> , | F) |

| a             | 1   | 1<br>2 | 1  | 2            | 2          | 2  |

| b             | 2   | 2      | 2  | 2            | 2          | 1  |

| $\mathcal{C}$ | 2   | 2      | 2  | 1            | 1          | 2  |

BY IDENTIFYING IDENTICAL COLUMNS OF SUCCESSORS, WE GET

$P_2 = (A, C, E) (B, D) (F)$

• SAME PROCESS TO OBTAIN THE NEXT PARTITION:

|               |              | 1  |    | 2            |     | 3   |

|---------------|--------------|----|----|--------------|-----|-----|

| $P_2$         | ( <i>A</i> , | С, | E) | ( <i>B</i> , | D), | (F) |

| a             | 1            | 1  | 1  | 3            | 3   |     |

| b             | 2            | 2  | 3  | 2            | 2   |     |

| $\mathcal{C}$ | 2            | 2  | 3  | 1            | 1   |     |

$$P_3 = (A, C) (E) (B, D) (F)$$

• SIMILARLY, WE DETERMINE  $P_4 = (A, C) (E) (B, D) (F)$

BECAUSE  $P_4 = P_3$  THIS IS ALSO THE EQUIVALENCE PARTITION P

## THE MINIMAL SYSTEM:

| PS | x = a | x = b   | x = c |

|----|-------|---------|-------|

| A  | E, 0  | B, 1    | B, 0  |

| B  | F, 0  | B, 0    | A, 1  |

| E  | A, 0  | F, 1    | F, 0  |

| F  | B,0   | A, 0    | F, 1  |

|    |       | NS, $z$ |       |

- THE STATE CODING IS CALLED *STATE ASSIGNMENT*

- CODING FUNCTIONS:

Input

$$C_I: I \to \{0,1\}^n$$

Output  $C_O: O \to \{0,1\}^m$

State  $C_S: S \to \{0,1\}^k$

Example 7.16

| PS | x = a | x = b   | x = c |

|----|-------|---------|-------|

| A  | E, 0  | B, 1    | B, 0  |

| B  | F, 0  | B, 0    | A, 1  |

| E  | A, 0  | F, 1    | F, 0  |

| F  | B, 0  | A, 0    | F, 1  |

|    |       | NS, $z$ |       |

## **BINARY CODING**

| In   | Input code Out |   | utput code |   | State | e assignment   |

|------|----------------|---|------------|---|-------|----------------|

| x(t) | $x_1(t)x_0(t)$ |   | z(t)       | ] | s(t)  | $s_1(t)s_0(t)$ |

| a    | 00             | 0 | 0          |   | A     | 00             |

| b    | 01             | 1 | 1          |   | B     | 01             |

| с    | 10             |   |            |   | E     | 10             |

|      |                |   |            |   | F     | 11             |

• THE RESULTING BINARY SPECIFICATION:

| $s_1(t)s_0(t)$ | $x_1 x_0 = 00$           | $x_1 x_0 = 01$ | $x_1 x_0 = 10$ |  |  |  |

|----------------|--------------------------|----------------|----------------|--|--|--|

| 00             | 10, 0                    | 01, 1          | 01, 0          |  |  |  |

| 01             | 11, 0                    | 01, 0          | 00, 1          |  |  |  |

| 10             | 00, 0                    | 11, 1          | 11, 0          |  |  |  |

| 11             | 01, 0                    | 00, 0          | 11, 1          |  |  |  |

|                | $s_1(t+1)s_0(t+1)$ , $z$ |                |                |  |  |  |

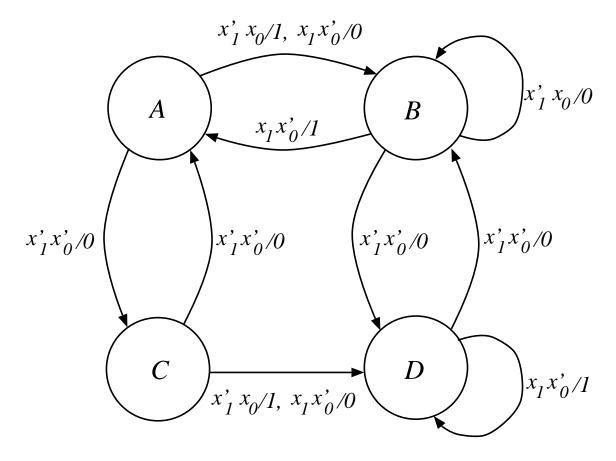

Figure 7.16: SWITCHING EXPRESSIONS AS ARC LABELS

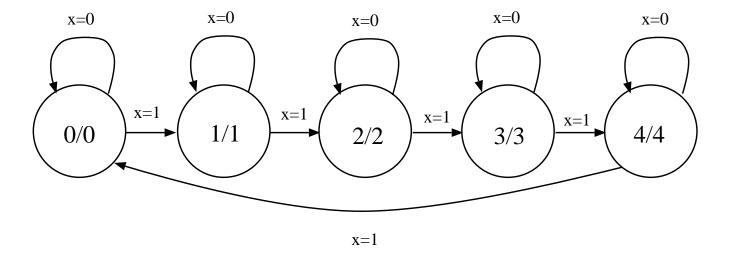

MODULO-p COUNTER: 0, 1, 2, ..., p-1, 0, 1, ...

$$z(t) = \left[\sum_{i=0}^{t} x(i)\right] \mod p$$

$$s(t+1) = \left[s(t) + x(t)\right] \mod p$$

$$z(t) = s(t) \text{ (if same coding)}$$

Figure 7.17: STATE DIAGRAM OF A MODULO-5 COUNTER

Figure 7.18: FRAGMENT OF STATE DIAGRAM OF PATTERN RECOGNIZER

Figure 7.19: STATE DIAGRAM OF A PATTERN RECOGNIZER